# **Technical Report**

# **Unified Overhead-aware Schedulability Analysis for Slot-based Task-splitting**

Paulo Baltarejo Sousa Konstantinos Bletsas Eduardo Tovar Pedro Souto Benny Akesson

CISTER-TR-130201

Version:

Date: 02-01-2013

# Unified Overhead-aware Schedulability Analysis for Slot-based Task-splitting

Paulo Baltarejo Sousa, Konstantinos Bletsas, Eduardo Tovar, Pedro Souto, Benny Akesson

CISTER Research Unit

Polytechnic Institute of Porto (ISEP-IPP)

Rua Dr. António Bernardino de Almeida, 431

4200-072 Porto

Portugal

Tel.: +351.22.8340509, Fax: +351.22.8340509

E-mail:

http://www.cister.isep.ipp.pt

#### Abstract

Hard real-time multiprocessor scheduling has seen, in recent years, the flourishing of semi-partitioned scheduling algorithms. This category of scheduling schemes combines elements of partitioned and migrative scheduling for the purposes of achieving efficient utilisation of the system's processing resources with strong schedulability guarantees and with low dispatching overheads. The sub-class of slot-based "task-splitting" scheduling algorithms, in particular, offers very good trade-offs between schedulability guarantees (in the form of high utilisation bounds) and the number of preemptions/migrations involved. However, so far there did not exist unified scheduling theory for such algorithms; each one was formulated in its own accompanying analysis. This article changes this fragmented landscape by formulating a unified schedulability theory for slot-based semi-partitioning in applicable to all known algorithms of this class. This new theory is based on exact schedulability tests, thus also overcoming many sources of pessimism in existing analysis. In turn, since schedulability testing guides the task assignment under the schemes in consideration, we also formulate an improved task assignment procedure. As the other main contribution of this article, and as a response to the fact thatmany unrealistic assumptions, present in the original theory, tend to undermine the theoretical potential of such scheduling schemes, we identified and modelled into the new analysis all overheads incurred by the algorithms in consideration. The outcome is a new overhead-aware schedulability analysis that permits increased efficiency and reliability. The merits of new theory are evaluated by an extensive set of experiments.

# Unified Overhead-aware Schedulability Analysis for Slot-based Task-splitting

Paulo Baltarejo Sousa  $\cdot$  Konstantinos Bletsas  $\cdot$  Eduardo Tovar  $\cdot$  Pedro Souto  $\cdot$  Benny Åkesson

Received: date / Accepted: date

Abstract Hard real-time multiprocessor scheduling has seen, in recent years, the flourishing of semi-partitioned scheduling algorithms. This category of scheduling schemes combines elements of partitioned and global scheduling for the purposes of achieving efficient utilization of the system's processing resources with strong schedulability guarantees and with low dispatching overheads. The sub-class of slot-based "task-splitting" scheduling algorithms, in particular, offers very good trade-offs between schedulability guarantees (in the form of high utilization bounds) and the number of preemptions/migrations involved. However, so far there did not exist unified scheduling theory for such algorithms; each one was formulated in its own accompanying analysis.

This article changes this fragmented landscape by formulating a more unified schedulability theory covering the two state-of-the-art slot-based semi-partitioned algorithms, S-EKG and NPS-F (both fixed job-priority based).

This new theory is based on exact schedulability tests, thus also overcoming many sources of pessimism in existing analysis. In turn, since schedulability testing guides the task assignment under the schemes in consideration, we also formulate an improved task assignment procedure. As the other main contribution of this article, and as a response to the fact that many unrealistic assumptions, present in the original theory, tend to undermine the theoretical potential of such scheduling schemes, we identified and modelled into the new analysis all overheads incurred by the algorithms in consideration. The outcome is a new overhead-aware schedulability analysis that permits increased

Paulo Baltarejo Sousa · Konstantinos Bletsas · Eduardo Tovar · Benny Åkesson CISTER/INESC-TEC, ISEP,

Polytechnic Institute of Porto, 4200-072 Porto, Portugal

$\hbox{E-mail: pbs@isep.ipp.pt}$

Pedro Souto ISR-Porto, FEUP,

University of Porto, Portugal E-mail: pfs@fe.up.pt

efficiency and reliability. The merits of this new theory are evaluated by an extensive set of experiments.

**Keywords** Multiprocessor Systems  $\cdot$  Slot-based Task-Splitting Algorithms  $\cdot$  Schedulability Analysis  $\cdot$  System Overheads

#### 1 Introduction

The advent of *multicore* chips has drawn the interest of the research community to real-time scheduling on multiprocessors<sup>1</sup> in order to allow efficient use of the processing capacity offered by such systems. However, many challenges exist, because, unlike real-time scheduling theory for uniprocessor systems, which is considered mature, real-time scheduling theory for multiprocessor systems is still a rapidly developing research field. One of the reasons behind many research challenges is that multiprocessor systems introduce an additional dimension to the scheduling problem, which is that of *task migration*. According to the degree of migration, multiprocessor scheduling algorithms have traditionally been categorized as *global* or *partitioned*.

Global scheduling algorithms store all tasks in one global queue, shared by all processors. At any time instant, the m highest-priority tasks among those are selected for execution on the m processors. Tasks can migrate from one processor to another during the execution; that is, an execution of a task can be stopped (preempted) in one processor and resumed on another processor. Some scheduling algorithms [9,3] of this class present a  $utilization\ bound$  (a metric for evaluating scheduling algorithms, defined as a threshold for the task set workload such that all tasks meet their deadlines when the task set workload does not exceed that threshold) of 100%, at the cost of many preemptions and migrations. However, the global shared queue imposes the use of some locking mechanism to serialize the access to that queue, which may become a bottleneck. Additionally, the high number of preemptions and migrations can cause numerous cache misses.

In contrast, partitioned scheduling algorithms partition the task set such that all tasks in a partition are assigned to the same processor. Tasks are not allowed to migrate from one processor to another. This class of scheduling algorithms presents a utilization bound of at most 50%. However, it transforms a multiprocessor system, composed by m processors, into m uniprocessor systems, thus simplifying the scheduling problem.

The partitioned scheduling schemes require two algorithms: an off-line task-to-processor assignment algorithm and a run-time task-dispatching algorithm. The first one assigns tasks to processors and the second one schedules tasks at run-time to execute on the processor(s). Assigning tasks to processors is a bin-packing problem, which is known to be NP-hard. The main goal of a bin-packing algorithm [20] is to pack a collection of items with different sizes

<sup>&</sup>lt;sup>1</sup> We use the term multiprocessor rather than multicore, because a lot of that work applies not only to multicore but also to other multiprocessor systems.

into the minimum number of fixed-size bins such that the total weight (or volume) in each bin does not exceed some maximum value. In the context of real-time scheduling algorithms, each item is a task from the task set, the size of each item is the *utilization of the task* (defined as the ratio between the execution requirement and the period or the minimal inter-arrival time of a task), each bin is a processor and the size of each bin is the processing capacity of one processor, usually assumed as 100%. There exist several heuristics for these types of problems; examples include Next-Fit (NF) and First-Fit (FF). NF assigns tasks one by one to the current processor and if one task does not fit on the current processor it leaves the current processor behind and continues packing on the next processor. FF assigns a task to the first (lowest indexed) processor that can accept the task. The task-dispatching algorithm schedules the statically assigned tasks using a uniprocessor scheduling algorithm, such as the Earliest-Deadline-First (EDF) [30], which assigns the highest priority to the ready task with earliest absolute deadline.

Recently, real-time researchers have developed semi-partitioned or task-splitting scheduling algorithms for multiprocessor systems to solve or reduce the drawbacks and limitations presented by global and partitioned scheduling algorithms. Typically, under task-splitting scheduling algorithms, most tasks (called non-split tasks) execute on only one processor (as in partitioning) while a few tasks (called split tasks) use multiple processors (as in global scheduling). Contrary to what the name may suggest, the code of such tasks is not split; what is split is the execution requirement of such tasks. This approach produces a better workload balance among processors than partitioning (and makes it possible to construct algorithms with a higher utilization bound). Additionally, semi-partitioning may be used to reduce (or remove [38]) the need for a locking mechanism (e.g. by avoiding global shared queues) and it has the potential to reduce the number of migrations, compared to global scheduling (by reducing the number of migrating tasks).

This article focuses on *slot-based* task-splitting scheduling algorithms. These scheduling algorithms present the highest utilization bound among scheduling algorithms that do not share a global queue. Such algorithms subdivide the time into (typically) equal-duration time slots. Each time slot on every processor is composed by one or more *time reserves*, which are time windows (of a fixed respective length) used to execute one or more tasks. Reserves for split tasks, which execute on two or more processors, must be carefully positioned within the time slots in order to avoid their overlapping in time. The three main contributions of the article are: (i) the formulation of a unified, processor demand-based and overhead-aware, schedulability analysis applicable to slot-based task-splitting algorithms S-EKG and NPS-F<sup>2</sup>; (ii) an improved task-assignment algorithm, taking advantage of the new analysis; and (iii) the identification of the overheads associated with slot-based task-splitting scheduling schemes. Apart from the theoretical value of the aforementioned contributions,

<sup>&</sup>lt;sup>2</sup> Specifically, we only cover the main variant of NPS-F, which splits tasks between no more than two processors.

they are also important because of the following real-world considerations. First, the higher processor utilization, resulting from the improved schedulability testing and task assignment, allows cost savings by enabling fewer (or slower) processors to schedule a given task set. Second, the overhead-aware nature of the analysis permits greater reliability, because it takes into account the overheads incurred by tasks when running in a real system. By contrast, analysis that ignore overheads may deem schedulable a task set, whose tasks may miss their deadlines when running in a real system because of the system overheads. This is an important step towards the use of task-splitting-based scheduling for higher-criticality applications (for which, a missed deadline may have serious real-world consequences).

#### 1.1 Historical perspective and related work

Semi-partitioning was born out of the desire to avert the occurrence of pathological cases when partitioned scheduling performed particularly inefficiently, such as in the following example.

**Example:** Consider m processors and n=m+1 tasks, each of which arrives every 2 time units and needs to execute for  $1.0 + \epsilon$  time units until its next arrival. With partitioning, there is no way to assign tasks without one processor being assigned two (or more) tasks. In turn, this means that on that processor, under whichever scheduling algorithm, it is impossible for more than one task to meet all its deadlines. The implication is that (for  $m \to \infty$  and  $\epsilon \to 0^+$ ) deadlines can be missed even though the system is utilized barely above 50%.

Yet, researchers observed [2,6] that, in many cases, if the execution time of a task could be "split" into two pieces (assigned to different processors), then it would be possible to meet deadlines. In the context of the above example, all tasks except the last one could be assigned to one respective processor but the last task could use two processors (any two) in the following manner: after each arrival, execute for  $(1.0 + \epsilon)/2$  time units on its first processor and the remaining  $(1.0 + \epsilon)/2$  time units on its second processor. Provided that the intervals for execution of this task on the two processors do not overlap in time, this would allow all deadlines to be met.

Many recent algorithms are based on this idea and they differ in: (i) how tasks are assigned to processors and split at design time; and (ii) how tasks (in particular, split tasks) are dispatched at run-time. In just a few years, the landscape of semi-partitioning already comprises many diverse approaches to scheduling. For example, see [2,6,26–28,4,5,29,15–18] and also the survey by Davis and Burns [21]. However, as mentioned before, this article focuses solely on the subset of slot-based task-splitting scheduling algorithms:

In 2006, Andersson and Tovar [6] introduced the first slot-based task-splitting scheduling algorithm called EKG (nowadays often retroactively referred to as "Periodic EKG" or "the original EKG"). EKG was limited to the scheduling of periodic tasks only. Under this scheme, time is divided into time

slots of unequal (in the general case) duration, with the time boundaries of a given time slot corresponding to the time instants of two consecutive job arrivals (possibly by different tasks) in the system. Most tasks are partitioned but at most m-1 tasks (with m being the number of processors) are split – each between a corresponding pair of successively indexed processors. Within each time slot, the first piece of a split task is executed at the end of the time slot on the first processor utilized by that task, and the second piece is executed at the start of the time slot on the other processor. All other tasks are executed under EDF on their respective processors. The basic form of the algorithm has a utilization bound of 100%. Clustered variants of EKG divide the system into m/k clusters of k processors each – hence the name EKG, stands for "EDF with task splitting and k processors in a group". Such clustering may be used to trade-off utilization bound for fewer preemptions and migrations.

However, the original EKG suffered from the limitation that, by design, it could not handle sporadically arriving tasks. This was because split task budgets in each time slot were proportional to the task utilization and the time slot length. However, given that time slots were formed between successive job arrivals, it was necessary to know the time of next job arrival in order to compute these budgets. With periodic tasks, this is not a problem, since arrival times are deterministic and may be computed in advance. However, with sporadic arrivals, this information is neither known in advance nor predictable.

This is why, in 2008, Andersson and Bletsas came up with an adapted design that came to be known as Sporadic EKG (S-EKG). In order to accommodate sporadic tasks, this algorithm "decouples" the time slot boundaries from the time instants of job arrivals. Rather, all time slots are of equal length. However, given that tasks can now arrive at "unfavorable" offsets relative to the time slot boundary, there is a penalty to be paid in terms of utilization bound: in order to ensure schedulability, processors can no longer be filled up to their entire processing capacity. Via a designer-set parameter, which controls the time slot length, S-EKG can be configured for a utilization bound from 65% to arbitrarily close to 100%, at the cost of more preemptions and migrations. Later in the same year, Andersson et al. came up with a version of S-EKG, named EDF-SS [5]. EDF-SS can handle arbitrary-deadline tasks (whereas its predecessor was formulated in the context of implicit-deadline tasks). However, due to different task assignment heuristics, one version does not dominate the other. Moreover, in part due to this "break" from the previous variant, no utilization bound above 50% has been proven for EDF-SS.

The three EKG variants discussed share a basic design: at most m-1 tasks are split, each between two successively indexed processors – the first piece of a split task executes at the end of the time slot on the first processor used by that task and the second piece is executed at the start of the time slot on the other processor. However, a less prescriptive approach to splitting the execution time of tasks between processors, while at the same time maintaining a slot-based dispatching, was soon devised:

In 2009, Bletsas and Andersson presented NPS [15], rapidly superseded entirely by NPS-F [16,17]. This algorithm (and its short-lived predecessor) employ a server-based approach. Each server (termed notional processor in the context of that work) serves one or more tasks employing an EDF scheduling policy. Under NPS-F (that stands for Notional Processor Scheduling - Fractional capacity), it is the execution time of these servers which is split – not directly that of the underlying tasks served. In principle, this allows improved efficiency in the utilization of a multiprocessor system. NPS-F has a utilization bound of 75% configurable up to 100% at cost of more preemptions and migrations. Compared to S-EKG, for corresponding configurations characterized by roughly the same number of preemptions, NPS-F has a higher utilization bound. However, a downside to splitting servers instead of tasks is that the number of migrating tasks is not bounded a priori and typically exceeds m-1.

#### 1.2 Contribution of this article

As a general pattern, not specific to semi-partitioned scheduling, scheduling theory tends to be originally formulated together with a set of simplifying assumptions that have little correspondence with a real system. In the context of slot-based task-splitting scheduling algorithms, although some practical works [35,36,38,13,39] have clearly demonstrated that these scheduling schemes are practical to implement in a real system, the practice also shows some performance degradation compared to what is theoretically achievable, due to various sources of overheads often unaccounted for by the theory. For instance, most theoretical works assume that task switching is instantaneous, but, in practice, it is time consuming because the operating system has to save the state of one task and restore that of another task. In this work, we bridge the gap between theory and practice by adapting the schedulability theory so that it accounts for the overheads that these algorithms incur in a real system. However, the contributions of the article are wider, and are outlined as follows:

- 1. We formulate a new and comprehensive scheduling theory for slot-based semi-partitioning. Although this theory is not specific to any particular scheme, we show how it can be applied to the specific algorithm under consideration (S-EKG or NPS-F). The fact that this new theory employs exact, processor demand-based, schedulability tests makes it inherently more efficient than the original analysis for the respective algorithms, which employed utilization-based tests. In the absence of overheads, the new analysis dominates its predecessors.

- 2. We identify and model into the new analysis all types of scheduling overheads manifested under the scheduling algorithms in consideration. This renders the new, unified schedulability analysis *overhead-aware*.

- 3. We develop a sophisticated off-line task assignment algorithm, which is guided by the new overhead-aware analysis. This brings increased efficiency and reliability to slot-based task-splitting scheduling algorithms.

4. We experimentally derive estimates of the various respective overheads using a real Linux-based multiprocessor system. Using these estimates we validate the efficiency and reliability of the new theory, by applying it to different scenarios.

Note however that, in this paper, we had to balance expressive completeness with presentation. Hence, strictly speaking, we only cover one of the two variants ("flat-mapped") of NPS-F, which, like S-EKG, the other algorithm covered, splits tasks between no more than two processors. Covering the general case (splitting over any number of processors) would add little practical value, since both NPS-F variants have the same theoretical properties, at the cost of considerable complexity. Another limitation of this work is that it does not consider the need for task synchronization (i.e. to access shared resources).

#### 1.3 Organization of this article

The remainder of this article is structured as follows. Section 2 discusses basic assumptions and the system model considered. A generic description of slot-based task-splitting algorithms is presented in Section 3 that ends with a summary of most of the notation used in this article. The purpose of this section is to provide the reader with the necessary background to understand the new demand-based and overhead-aware schedulability analysis presented in Section 4. This analysis is then used to develop a new task to processor assignment algorithm in Section 5. In Section 6, the new schedulability analysis is evaluated and compared to the original schedulability analysis of slot-based task-splitting scheduling algorithms. Additionally, extensive experimental results are provided and discussed. Finally, in Section 7 conclusions are drawn.

#### 2 Assumptions and system Model

#### 2.1 Assumptions about the architecture

We assume a multiprocessor system consisting of identical processors, all of which always execute at the same frequency. This means that the *execution speed* of a processor does not depend on activities on another processor (e.g. whether the other processor is busy or idle or which task it is busy executing) nor does it change at run-time. This work is therefore only applicable to systems with Simultaneous MultiThreading (SMT) and Dynamic Voltage and Frequency Scaling (DVFS) features disabled. In state-of-the-art hardware it is possible to disable both these hardware features via the BIOS and/or software.

We assume that each processor has a *local timer* that keeps track of realtime (not calendar time) and provides a function for reading its value. Furthermore, we assume that it is able to generate an interrupt at x time units in the future (x being configurable). These facilities are rather common. For example, on Linux they are provided by the high-resolution timers framework.

#### 2.2 System model

We consider preemptive real-time systems composed by m physical processors. Each physical processor is uniquely indexed in the range  $P_1 \cdots P_m$ . The system also includes a task set  $\tau$  composed by n independent tasks, each of which is uniquely indexed in the range  $\tau_1 \cdots \tau_n$ . Each task  $\tau_i$  is characterized by its worst-case execution time  $C_i$ , by its minimum inter-arrival time  $T_i$  and by the time span that can elapse since its arrival until its execution is completed, the relative deadline  $D_i$ . We assume  $0 \le C_i \le D_i$ . Note that we also assume arbitrary deadlines, i.e. it may be that  $D_i < T_i$ ,  $D_i = T_i$  or  $D_i > T_i$ .

The utilization of task  $\tau_i$ , denoted  $u_i$ , is defined as:

$$u_i = \frac{C_i}{T_i} \tag{1}$$

and the (normalized) system utilization,  $U_s$ , is defined as:

$$U_s = \frac{1}{m} \cdot \sum_{i=1}^n u_i \tag{2}$$

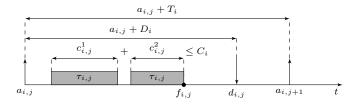

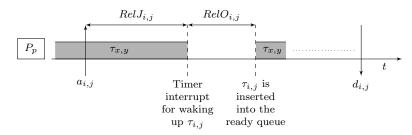

Each task  $\tau_i$  generates a potentially infinite number of jobs and each job  $\tau_{i,j}$  (that is the  $j^{th}$  job of task  $\tau_i$  with  $j \leq 1$ ) becomes ready to be executed at arrival time  $(a_{i,j})$  and continues until finishing (or completion) time  $(f_{i,j})$ . The absolute deadline  $(d_{i,j})$  of job  $\tau_{i,j}$  is computed as  $d_{i,j} = a_{i,j} + D_i$  and a deadline miss occurs when  $f_{i,j} > d_{i,j}$ . By definition of  $T_i$ , the time difference between any two consecutive job arrivals must be at least equal to  $T_i$ . Figure 1 illustrates the relation among the timing parameters of job  $\tau_{i,j}$ . The execution of job  $\tau_{i,j}$  is represented by a gray rectangle and the sum of all execution chunks  $(c_{i,j}^x)$  must be less or equal than  $C_i$ .

Fig. 1: Job timing parameters.

We also consider a set of k servers, which are equivalent to physical processors in terms of processing capacity, indexed in the range  $\tilde{P}_1 \cdots \tilde{P}_k$ . The set of tasks that can be assigned to a server  $\tilde{P}_q$  (denoted by  $\tau[\tilde{P}_q]$ ) is limited by its processing capacity that is equal to 1.0 (100%). The utilization of a server  $\tilde{P}_q$  ( $U[\tilde{P}_q]$ ) is given by:

$$U[\tilde{P}_q] = \sum_{\tau_i \in \tau[\tilde{P}_q]} u_i \tag{3}$$

#### 3 Slot-based task-splitting

This section provides background on slot-based semi-partitioning that is essential to understand the demand-based and overhead-aware schedulability analysis presented in the next section. We start by describing the basic concepts and a generic scheduling algorithm. We then show that both S-EKG<sup>3</sup> and NPS-F can be formulated as instances of this generic algorithm.

From this point onwards, we will not consider the (original) EKG scheduling algorithm [6], whose applicability is limited to periodic task sets with implicit deadlines, and whenever we refer to slot-based task-splitting algorithms we mean S-EKG and NPS-F.

#### 3.1 Generic scheduling algorithm

A key concept of the generic scheduling algorithm is that of a server. A server is a logical entity that provides computation services to tasks and has a maximum capacity equal to that of the underlying physical processors. Thus, in the generic algorithm, a task is first mapped to a server, which is then allocated one or two processors. A processor may be allocated to at most three servers, but at any time a processor is allocated to only one server and one server is served by at most one processor. A time reserve is a time window during which a processor is exclusively reserved to a server, i.e. executes tasks of only that server. Therefore, time reserves on a processor are non-overlapping. Furthermore, given the sporadic nature of the tasks in a server, time reserves are periodic and we call their period, which is the same for all reserves, the time slot. In the generic scheduling algorithm, in any time slot, a processor has one time reserve per server it is allocated to.

The scheduling of a set of tasks in the generic algorithm comprises two procedures, one that is performed off-line and another that is executed at runtime. The off-line procedure maps tasks to servers, determines the computation capacity of each server and allocates reserves on the processors in order to ensure that each server has the required capacity. The run-time procedure should be a scheduling algorithm that runs on each processor and that uses EDF to choose the task of the server associated to the currently active time reserve.

We now describe the off-line procedure. The generic algorithm specifies a procedure composed of four steps and what is performed in each step, but it does not prescribe any algorithm for any of the steps. This is up to the specific scheduling algorithms.

To illustrate the generic algorithm, we use an example. The figures illustrating its application were obtained by using the algorithms specified for the NPS-F, later described in Section 3.3. The task set  $(\tau)$  in our example is com-

<sup>&</sup>lt;sup>3</sup> We focus on S-EKG and not in EDF-SS, because latter is a version of the former that explores different bin-packing heuristics for assigning task-to-processors.

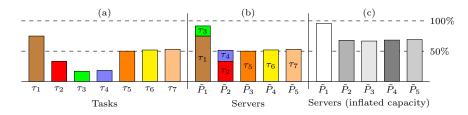

prised of seven tasks,  $\tau_1$  to  $\tau_7$ . Inset (a) of Figure 2 represents each task in that set by a rectangle whose height represents that task's utilization.

The first step of the off-line procedure is mapping tasks to servers, which we denote  $\tilde{P}_q$ . The generic algorithm does not prescribe how tasks are mapped to servers. Each specific scheduling algorithm can use its own mapping. Inset (b) of Figure 2 shows the task-to-server mapping obtained by applying NPS-F's first step algorithm.

Fig. 2: Task-to-server mapping.

The second step of the off-line procedure is to determine the (computation) capacity of each server. This is obtained by *inflating* the sum of the utilization's of the server's tasks. Capacity inflation is required to compensate for time intervals during which a server may have ready tasks, but none of them can be executed. Such a scenario may arise because none of the server's time reserves are active, and a processor executes tasks of only the server associated to its current time reserve. Several methods can be used to determine by how much to inflate a server capacity. In Section 4, we present one method in the context of the new schedulability analysis. At this point, we assume that such a method exists, and illustrate its application in Inset (c) of Figure 2.

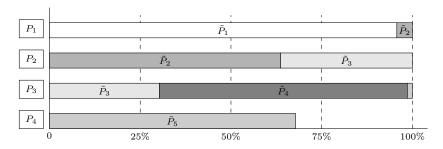

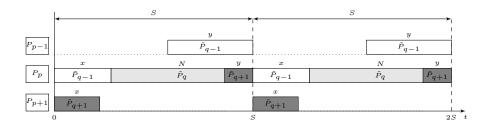

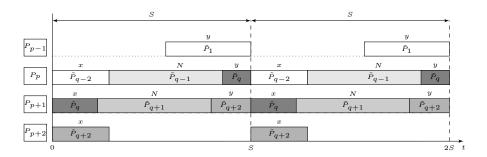

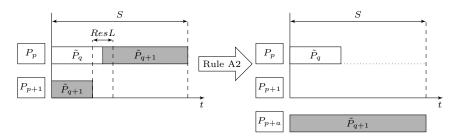

The third step of the off-line procedure is to allocate processors to servers. Again, the generic algorithm does not prescribe how this allocation is done. Each specific algorithm can specify its own. Figure 3 illustrates the server-to-processor assignment obtained by applying the algorithm used in NPS-F to our running example. Servers  $\tilde{P}_1$  and  $\tilde{P}_4$  are assigned to only one processor each, and are, hence, classified as non-split servers; whereas servers  $\tilde{P}_2$ ,  $\tilde{P}_3$ , and  $\tilde{P}_5$  are split servers because they are assigned to two processors each.

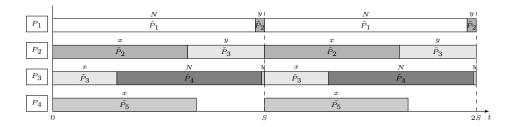

The fourth and last step of the off-line procedure is to define the reserves for each processor. Again, the generic algorithm does not prescribe how this is done. Figure 4 illustrates the reserves determined by the application of an algorithm used by NPS-F to our running example. In this case, all processors synchronize at the beginning of each time slot. However, other schemes are possible, as shown in Section 4. On each processor  $P_p$ , the time slot can be divided into three reserves, at most:  $x[P_p]$ ,  $y[P_p]$ , and  $N[P_p]$ . The  $x[P_p]$  reserve occurs at the beginning of the time slot and it is reserved for the split server shared by processor  $P_p$  and processor  $P_{p-1}$ , if any. The  $y[P_p]$  reserve occurs at the end of the time slot and it is reserved for the split server shared by processor

Fig. 3: Server-to-processor assignment

$P_p$  and processor  $P_{p+1}$ , if any. The remaining part,  $N[P_p]$ , is reserved for the non-split server assigned to processor  $P_p$ .

Fig. 4: Processor reserves and time slot.

At run-time, the dispatching inside each reserve is performed according to an Earliest-Deadline First (EDF) policy: the active job with the earliest deadline, among those served by the reserve is executed.

#### 3.2 S-EKG

The S-EKG algorithm shares many features with the generic algorithm. Both are slot-based; both use an off-line procedure to map tasks to processors and a run-time algorithm that uses EDF to choose the running task. A major difference between the two is that S-EKG, as described in its original publication [4], does not use the concept of server, instead it assigns tasks to processors directly, employing a procedure similar to the NF bin-packing heuristic that we describe next.

In S-EKG, the task-to-processor mapping procedure strives to ensure that the utilization of each processor is equal to  $UB_{S-EKG}$  (a theoretical utilization bound of the algorithm). It iterates over the set of tasks. If a task has a utilization that exceeds  $UB_{S-EKG}$ , it assigns the task to a dedicated processor. Otherwise, it assigns the task to the next available processor whose utilization

is lower than  $\mathrm{UB_{S-EKG}}$ . In this case, if task  $\tau_i$  cannot be integrally assigned to the current processor,  $P_p$ , without exceeding that bound, it is split between that processor and the next one,  $P_{p+1}$ , so that  $P_p$  ends up utilized exactly by  $\mathrm{UB_{S-EKG}}$  and  $P_{p+1}$  receives the remaining share of  $\tau_i$ . Consequently, the number of split tasks is at most m-1 and there is at most one task split between each pair of successively indexed processors  $P_p$  and  $P_{p+1}$ . Furthermore, in a schedulable system, the utilization of every non-dedicated processor (except possibly the last one) is exactly  $\mathrm{UB_{S-EKG}}$ .

S-EKG uses a designer-set integer parameter  $\delta$ , which determines the length of the time slot according to Equation 4.

$$S = \frac{1}{\delta} \min_{\tau_i \in \tau} (T_i) \tag{4}$$

This parameter also affects the utilization bound ( $UB_{S-EKG}$ ) and the inflation factor ( $\alpha$ ), which is used to inflate the utilization, as follows:

$$UB_{S-EKG} = 4 \cdot (\sqrt{\delta \cdot (\delta + 1)} - \delta) - 1$$

(5)

$$\alpha = \frac{1}{2} - \sqrt{\delta \cdot (\delta + 1)} + \delta \tag{6}$$

Depending on the chosen value for  $\delta$ , UB<sub>S-EKG</sub> varies from 65% (with  $\delta$  equal to one) to arbitrarily close to 100% (for  $\delta \to \infty$ ). Therefore, the value of  $\delta$  can be used to trade-off the target utilization bound against preemptions and migrations.

Although, the original description of S-EKG [4] does not use the concept of server, it is straightforward to map tasks to servers, which are then allocated time reserves as done in the generic algorithm, in such a way that each task is allocated the same set of processors as in S-EKG. The rules to apply are as follows: (i) each task assigned to a dedicated processor is mapped to a server, which is then allocated exclusively the same dedicated processor as in S-EKG; (ii) all non-split tasks that are assigned to one processor are mapped to a non-split server, which is then allocated the same processor as in S-EKG; (iii) each split task is mapped to a server that is split between the same processors that split task is assigned to in S-EKG.

With respect to the inflation of servers, under the original approach [4], each server is (safely, but inefficiently) inflated by the same amount  $2 \cdot \alpha$  – in other words:

$$U_{S-EKG}^{infl:orig}[\tilde{P}_q] = U[\tilde{P}_q] + 2 \cdot \alpha \tag{7}$$

with  $\alpha$  calculated according to Equation 6.

#### 3.3 NPS-F

It is rather straightforward to formulate NPS-F as an instance of the generic algorithm. Indeed, NPS-F is based on the same concepts as the generic algorithm, and these concepts even have the same name, except for the servers,

which were called "notional processors", and gave the name to NPS-F. Furthermore, NPS-F's off-line procedure comprises exactly the same four steps.

Next, we summarize the algorithms used by NPS-F for each step of the off-line procedure. These are the algorithms that were used in the running example in Section 3.1 to illustrate the generic algorithm.

In the first step, the mapping of tasks to servers, NPS-F uses any binpacking heuristic so that the utilization of each server is smaller or equal to that of a processor. Inset (b) of Figure 2, in Section 3.1, shows the taskto-server mapping obtained with NPS-F by employing the FF bin-packing heuristic.

In the second step, the original paper on NPS-F used the following expression to inflate the capacity of each of the servers obtained in the first step:

$$U_{NPS-\tilde{F}}^{infl:orig}[\tilde{P}_q] = \frac{(\delta+1) \cdot U[\tilde{P}_q]}{U[\tilde{P}_q] + \delta}$$

(8)

where  $\delta$  is an integer designer-set parameter, which is also used to set the length of the time slot like in S-EKG (see Equation 4).

The algorithm used by NPS-F to allocate processors to servers, the third step, just iterates over the set of servers and assigns each server to the next processor that has yet some available capacity. If the processor's available capacity cannot accommodate the processing requirements of a server, the server is *split*. That is, the current processor's available capacity is allocated to partially fulfil the server's requirements, whereas the server remaining requirements are fulfilled by the next processor.

Finally, the algorithm used by NPS-F in the fourth and last step is also straightforward. For each processor, it allocates one reserve per server. Furthermore, the duration of each reserve is proportional to the processor capacity used by the corresponding server and is such that each server is periodic with a period equal to the time slot, S.

We end this subsection with the utilization bound determined by the original schedulability analysis:

$$UB_{NPS-F} = \frac{2 \cdot \delta + 1}{2 \cdot \delta + 2} \tag{9}$$

which ranges from 75% (for  $\delta$  equal to one, which is the most preemption- and migration-light setting) to arbitrarily close to 100% (for  $\delta \to \infty$ ). Because  $\delta$  controls the length of the time slot, S, (see Equation 4), its value can be used to trade-off the target utilization bound against preemptions and migrations like in S-EKG.

#### 3.4 Notation

For ease of reference, Table 1 provides a summary of most of the notation used in this article.

Table 1: Notation

| Table 1: Notation                                 |                                                                         |                                                                         |

|---------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Symbol                                            | Interpretation                                                          | $egin{array}{c} \mathbf{Constraint}/ \ \mathbf{Definition} \end{array}$ |

| $\tau$                                            | A task set                                                              |                                                                         |

| $	au_i$                                           | The $i^{th}$ task                                                       |                                                                         |

| $C_i$                                             | The worst-case execution requirement of task $\tau_i$                   |                                                                         |

| $T_i$                                             | The minimum inter-arrival time of task $\tau_i$                         | $T_i \ge C_i$                                                           |

| $D_i$                                             | The relative deadline of task $\tau_i$                                  | $D_i \ge C_i$                                                           |

| $u_i$                                             | The utilization of task $\tau_i$                                        | $u_i = C_i/T_i$                                                         |

| n                                                 | The number of tasks of $\tau$                                           |                                                                         |

| ${	au_{i,j}}$                                     | The $j^{th}$ job of task $\tau_i$                                       |                                                                         |

| $a_{i,j}$                                         | The arrival time of job $\tau_{i,j}$                                    |                                                                         |

| $d_{i,j}$                                         | The absolute deadline of job $\tau_{i,j}$                               | $d_{i,j} = a_{i,j} + D_i$                                               |

| $P_p$                                             | The $p^{th}$ processor                                                  |                                                                         |

| $x[P_p]$                                          | The processor $P_p$ 's $x$ reserve length                               | See Equation 39                                                         |

| $N[P_p]$                                          | The processor $P_p$ 's $N$ reserve length                               | See Equation 39                                                         |

| $y[P_p]$                                          | The processor $P_p$ 's y reserve length                                 | See Equation 39                                                         |

| $U[P_p]$                                          | The utilization of processor $P_p$                                      |                                                                         |

| $\frac{m}{	ilde{P}_q}$                            | The number of processors  The $q^{th}$ server                           |                                                                         |

|                                                   |                                                                         |                                                                         |

| $	au[	ilde{P}_q]$                                 | The set of tasks assigned to the server $\tilde{P}_q$                   | C                                                                       |

| $U[P_q]$                                          | The utilization of server $P_q$                                         | See Equation 3                                                          |

| $U^{infl}[\tilde{\tilde{P}}_q]$                   | The inflated utilization of server $\tilde{P}_q$                        | See Algorithm 2                                                         |

| $U_x^{infl}[	ilde{P}_q] \ U_y^{infl}[	ilde{P}_q]$ | The $x$ part of the inflated utilization of server $P_q$                | See Equation 39                                                         |

| $U_y^{inj}[P_q]$                                  | The $y$ part of the inflated utilization of server $\tilde{P}_q$        | See Equation 39                                                         |

| $\frac{k}{S}$                                     | The number of servers                                                   | G D 4: 4                                                                |

| S                                                 | The time slot length A designer-set integer parameter controlling the   | See Equation 4                                                          |

| $\delta$                                          | migration frequency of split tasks                                      |                                                                         |

| $\alpha$                                          | The inflation factor of S-EKG                                           | See Equation 4                                                          |

|                                                   | The time interval between the two split server                          | *                                                                       |

| $\Omega$                                          | reserves                                                                | See Equation 38                                                         |

| RelJ                                              | An upper bound for the release jitter                                   | See Figure 5                                                            |

| RelO                                              | An upper bound for the release overhead                                 | See Figure 5                                                            |

| ResL                                              | An upper bound for the reserve latency                                  | See Figure 7                                                            |

| CtswO                                             | An upper bound for the context switch overhead                          |                                                                         |

| IpiL                                              | An upper bound for inter-processor interrupt latency                    | See Figure 8                                                            |

| CpmdO                                             | An upper bound of the cache-related preemption/migration delay overhead |                                                                         |

| - faha                                            | Execution time of the fake task modelling a                             | See Equation 27                                                         |

| $C^{fake}$                                        | reserve                                                                 | and Equation 40                                                         |

| $D^{fake}$                                        | Deadline of the false took                                              | See Equation 27                                                         |

| $D^*$                                             | Deadline of the fake task                                               | and Equation 40                                                         |

| $T^{fake}$                                        | Minimal inter-arrival time of the fake task                             | See Equation 27                                                         |

|                                                   |                                                                         | and Equation 40                                                         |

| $U_s$                                             | Utilization of the system                                               | See Equation 2                                                          |

| $UB_{S-EKG}$                                      | Utilization bound of S-EKG                                              | See Equation 5                                                          |

| $UB_{NPS-F}$                                      | Utilization bound of NPS-F                                              | See Equation 9                                                          |

## $4\ \mathrm{New}$ demand-based and overhead-aware schedulability analysis

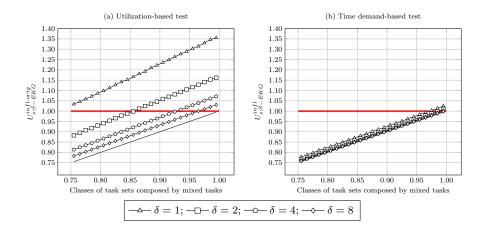

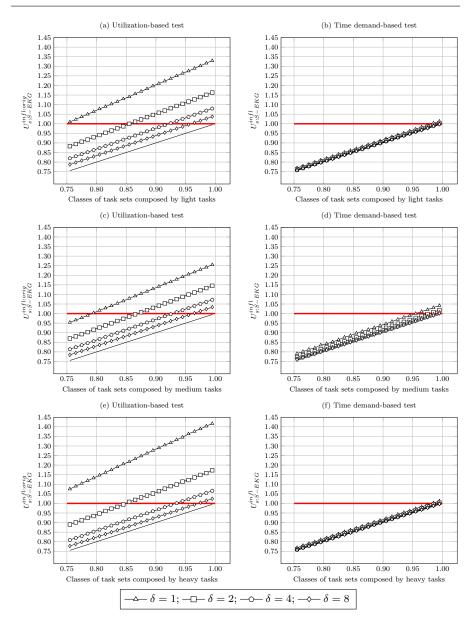

The original schedulability analysis for slot-based task-splitting scheduling algorithms was based on utilization. While this simplifies the derivation of utilization bounds, it also entails pessimism. In [5], the move towards processor-demand based analysis was not carried out in a way that would preserve the most useful theoretical properties (namely, the utilization bound) of previous work (S-EKG). Therefore, in [37], the authors present a schedulability analysis based on processor demand specific for the S-EKG scheduling algorithm.

In this article, a new schedulability analysis, based on processor demand, is introduced that can be applied to both S-EKG and NPS-F. This new schedulability analysis supersedes all previous utilization-based analyses. Further, it defines new schedulability tests that incorporate all real-world overheads incurred by implementations of the S-EKG and NPS-F algorithms [38,39].

The schedulability analysis that we develop in this section has two stages, which correspond to the two main stages of the task-to-processor mapping algorithm presented in the previous section. In the first stage, the analysis focuses on the schedulability of the tasks assigned to each server, assuming that each server is executed in isolation on a processor. The second stage examines whether there is enough capacity to accommodate all servers in the system.

We present each stage of the new demand-based overhead-aware schedulability analysis in its own subsection, but before that we provide an overview of the overheads that may be incurred by this class of scheduling algorithms.

#### 4.1 Overheads

In order to carry out an overhead-aware schedulability analysis, we first need to identify the overheads that may be incurred at run-time because of the mechanisms used in the implementation of the scheduling algorithms. In this subsection, we provide an overview of the overheads that may arise in an implementation of a slot-based task-splitting scheduling algorithm. This overview is based on implementations [38,39] of S-EKG and NPS-F in the Linux kernel for the x64 architecture.

The overheads that a system may incur because of a scheduling algorithm are related to the following five mechanisms: (i) interrupts; (ii) timers; (iii) ready queues; (iv) context switching; and (v) caches. We examine the overheads of each mechanism in turn.

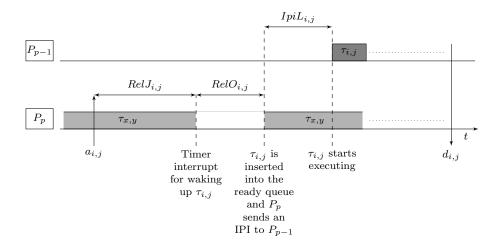

Most real-time systems interact with their environment and use interrupts whenever they need to react to external events. We assume that the interrupt handlers, or interrupt service routines, are implemented as tasks, as supported in the PREEMPT-RT Linux kernel [32]. Nevertheless, the occurrence of an interrupt suspends the execution of the currently running task to release a task that will service this interrupt. Furthermore, depending on the deadline of the released task, it may preempt the currently running task. A special kind of interrupt is the inter-processor interrupt (IPI). As its name suggests, these interrupts are generated by one processor and handled on another, and may be used by a processor to notify another of the occurrence of events. The processing of an IPI by the target processor is similar to that of an interrupt generated by the environment. Our algorithms use the IPI in the implementation of split servers, more specifically when a job, whose priority is higher than that of all ready jobs of its server, arrives on a processor at a time instant that falls within the reserve of that server in the other processor. In this case, the newly arrived job should immediately start execution in the server's reserve

on the other processor. We denote the delay incurred by the use of IPI in the dispatching of a task the *IPI Latency*, *IpiL*.

Timers are a per-processor mechanism of the Linux kernel designed to schedule computations some time in the future. Our algorithms use timers to release tasks and also to trigger "server-switches" at the end of each time reserve. Timers are implemented using a priority queue and interrupts generated by some timer/counter device, therefore they incur overheads related to the handling of these interrupts as well. Timer interrupts are different from other interrupts in that they are not handled by separate tasks, but immediately upon occurrence of the interrupt. Thus, the expiration of a timer suspends the execution of the current task on that processor. Another "imperfection" associated with timers is that they cannot be used to measure time intervals precisely. We denote the delay incurred in the release of periodic tasks because of these imperfections the *Release Jitter*, *Rel J*.

The kernel keeps the released tasks that are ready to run in queues, known as ready queues. Therefore, when a task is released, the scheduler moves the task to a ready queue, and the dispatcher is invoked to select the next task to run, which may be either the task that was running before the release of the task, the released task or any other task that is ready to run. In the case of the slot-based task-splitting algorithms considered, all these data structures are either private to some processor or shared by two processors. Nevertheless, the release of a task requires some processing, which we call the *Release Overhead*, *RelO*.

A context switch occurs whenever the dispatcher decides to change the running task on a processor. This entails saving the state of the processor to some operating system data structure associated with the task being evicted, and restoring the state of the processor to the contents of the corresponding data structure associated with the task that was allocated the processor. We use the *Context switch Overhead*, *CtswO*, to account for this overhead.

The worst-case execution time of a task is very hard to estimate for processors with caches. For this reason, if any memory caching mechanism is used at all, locked caches or scratchpads are often used instead in the embedded domain, for better predictability [8,33]. Still, in this work we assume the use of conventional caches, as in general-purpose processors. For such architectures, the worst-case execution time of a task is typically computed assuming that the task is executed without being preempted. However, when a task is preempted, it may incur additional costs when it is resumed because the cache lines with its data may have been evicted by other tasks and need to be fetched again from main memory, or from higher cache levels. Likewise, migrating one task from one processor to another requires the destination processor to fetch anew the cache footprint of the task. These costs are known as cache-related preemption and migration delays (CPMD). To incorporate the CPMD, we pessimistically assume that every preemption incurs the worst-case CPMD cost, CpmdO. Furthermore, we do not distinguish between job preemption and job migration events. This simplification is not as pessimistic as it may seem because there is evidence [12,14] to suggest that, in a heavily loaded system, the

CPMD costs of preemptions and migrations can be similar. Another simplification is that we do not differentiate between tasks when applying CPMD costs; we use the same cost CpmdO irrespective of the preempted or the preempting task. Although some works [25,31] allow for estimating CPMD more precisely, they rely on detailed knowledge of the program code of each task and the memory layout.

Although in this subsection we have identified the different sources of overheads associated with slot-based task-splitting scheduling algorithms, in the analysis devised in the subsequent subsections, we sometimes lump together overheads of different sources that occur in sequence. The reasons for this are two-fold. First, this leads to shorter expressions. Second, it simplifies the experimental measurement of the overheads and often leads to more precise experimental estimates of these overheads.

#### 4.2 New demand-based schedulability test for mapping tasks to servers

In this section, we derive a schedulability test for the tasks mapped to a server based on demand-bound functions that takes into account the overheads described in the previous subsection. This leads to a new task-to-server mapping algorithm. For the purpose of the mapping of tasks to servers, we consider that a server is allocated a processor exclusively, i.e. it runs on a single processor that it does not share with any other server. Hence, we treat each server as a uniprocessor system.

Our analysis is based on the concept of demand-bound function (dbf) [10], which specifies an upper bound on the aggregate execution requirements of all jobs (of  $\tau[\tilde{P}_q]$ ) over any possible interval of length t. Therefore the demand-based schedulability test for a server  $\tilde{P}_q$  is given by:

$$dbf^{part}(\tilde{P}_q, t) \le t, \forall t > 0$$

(10)

We use the word "part", which stems from "partitioned", as a superscript of all the dbfs of this stage to distinguish them from functions of the second stage.

Ignoring all overheads and assuming sporadic task sets with arbitrary deadlines, the  $\mathrm{dbf}^{\mathrm{part}}(\tilde{P}_q,t)$  can be computed as:

$$dbf^{part}(\tilde{P}_q, t) = dbf^{part}(\tau[\tilde{P}_q], t) = \sum_{\tau_i \in \tau[\tilde{P}_q]} \max\left(0, \left\lfloor \frac{t - D_i}{T_i} \right\rfloor + 1\right) \cdot C_i \quad (11)$$

Next, we proceed by incorporating each source of overhead into the new overhead-aware schedulability analysis, one at a time. First, we consider the overheads caused by the release of tasks. We assume that all tasks are periodic, because it corresponds to the worst case. For periodic tasks we need to take into account not only the release overhead, but also the release jitter caused by

timers. Therefore, the effects of timers and task release will be considered together. Next, we consider the effects of context switching and CPMD. Finally, we incorporate the effect of interrupts other than those caused by timers.

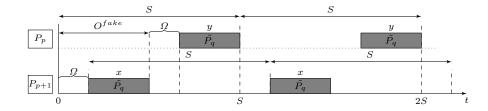

Scheduling algorithms use timers to trigger the release of periodic tasks. Therefore, the release of periodic tasks is affected by two of the overheads discussed in the previous section: the release overhead, and the release jitter. Figure 5 graphically shows these two overheads for job  $\tau_{i,j}$ . (In all figures, the execution of a job is graphically represented by a rectangle labelled with the job identifier.) As illustrated, the effects of these two overheads are different. Whereas both overheads, the release jitter of job  $\tau_{i,j}$ ,  $RelJ_{i,j}$ , and the release overhead of job  $\tau_{i,j}$ ,  $RelO_{i,j}$ , reduce the amount of time that job  $\tau_{i,j}$  has to complete its execution, only the release overhead actually requires processing time. Thus, we model the effect of these two overheads differently.

Fig. 5: Illustration of the release jitter and release overhead. In this example,  $\tau_{x,y}$  is the currently executing job that incurs an execution penalty due to the release overhead  $RelO_{i,j}$  of job  $\tau_{x,y}$ .

Let RelJ and RelO be the upper bounds on the release latency and on the release overhead, respectively. As shown in Figure 5, the release latency decreases the amount of time available to complete a task, i.e., in the worst case,  $\tau_i$  has  $D_i - RelJ$  time units to complete. Therefore, we modify the dbf<sup>part</sup> $(\tau[\tilde{P}_q], t)$  to:

$$dbf^{part}(\tau[\tilde{P}_q], t) = \sum_{\tau_i \in \tau[\tilde{P}_q]} \max\left(0, \left\lfloor \frac{t - (D_i - RelJ)}{T_i} \right\rfloor + 1\right) \cdot C_i$$

(12)

Concerning the release overhead, one way of modelling it could be by increasing the execution demand of a task accordingly. However, that approach does not work properly when multiple tasks are released too close together in time. The reason is that the release overhead contributes "immediately" to the processor demand – meaning that to model the processor demand correctly, it should be increased by RelO time units at the time of the release, not at the deadline of the task released. Therefore, we instead model the release overhead as higher-priority interfering workload (as it is in reality). This way, we may

compute the execution demand for releasing all jobs of  $\tau[\tilde{P}_q]$  in a time interval  $[1,\,t)$  as:

$$dbf_{RelO}^{part}(\tau[\tilde{P}_q], t) = \sum_{\tau_i \in \tau[\tilde{P}_q]} \left\lceil \frac{t + RelJ}{T_i} \right\rceil \cdot RelO$$

(13)

Modifying accordingly  $dbf^{part}(\tau[\tilde{P}_q], t)$ , we get:

$$dbf^{part}(\tau[\tilde{P}_q], t) = dbf^{part}_{RelO}(\tau[\tilde{P}_q], t) + \sum_{\tau_i \in \tau[\tilde{P}_q]} \max\left(0, \left\lfloor \frac{t - D_i + RelJ}{T_i} \right\rfloor + 1\right) \cdot C_i \quad (14)$$

We now consider the context switching overhead, which is common to all schedulers. Every job causes at most two context switches: when it is released and when it completes – but not every job release causes a context switch. Therefore the number of context switches over a time interval of length t is upper bounded by twice the number of job releases during that interval. Let CtswO be an upper bound on the context switch overhead. We amend the derivation of the dbf<sup>part</sup> $(\tau[\tilde{P}_q],t)$ , by increasing the execution demand of each job by twice CtswO, to:

$$dbf_{\text{RelO}}^{\text{part}}(\tau[\tilde{P}_{q}], t) = dbf_{\text{RelO}}^{\text{part}}(\tau[\tilde{P}_{q}], t) + \sum_{\tau_{i} \in \tau[\tilde{P}_{q}]} \max\left(0, \left\lfloor \frac{t - D_{i} + RelJ}{T_{i}} \right\rfloor + 1\right) \cdot (C_{i} + 2 \cdot CtswO)$$

(15)

In order to incorporate the cache-related overheads, i.e. the CPMD, we assume that every preemption incurs the worst-case CPMD cost, CpmdO. Furthermore, we compute an upper bound on the number of preemptions for server  $\tilde{P}_q$  in a time interval of length t as:

$$\operatorname{nr}_{\operatorname{pree}}^{\operatorname{part}}(\tilde{P}_q, t) = \sum_{\tau_i \in \tau[\tilde{P}_q]} \left\lceil \frac{t + \operatorname{Rel}J}{T_i} \right\rceil \tag{16}$$

That is, we assume that every task that may be released by a timer in a time interval of length t, causes a preemption. Thus, the cumulative cost of CPMD over one interval of length t is:

$$dbf_{CpmdO}^{part}(\tilde{P}_q, t) = nr_{pree}^{part}(\tilde{P}_q, t) \cdot CpmdO$$

(17)

Because this increases the server execution demand, we amend the expression of the  $\mathrm{dbf}^{\mathrm{part}}(\tilde{P}_q,t)$  (Equation 15) to:

$$dbf^{part}(\tilde{P}_q, t) = dbf^{part}(\tau[\tilde{P}_q], t) + dbf^{part}_{CpmdO}(\tilde{P}_q, t)$$

(18)

In contrast with the other overheads, the cache related overheads cannot be assigned to a particular task. Indeed, the jobs of some tasks may never

be preempted, whereas the jobs of other tasks may be preempted several times. This is the reason why we do not incorporate the CPMD overheads in  $\mathrm{dbf}^{\mathrm{part}}(\tau[\tilde{P}_q],t)$ .

Finally, we consider the interrupt overheads. We assume that interrupt service tasks have higher priority than "normal" tasks. Thus, we model each sporadic interrupt as a task with worst-case execution time equal to  $C_i^{Int}$ , minimum inter-arrival time equal to  $T_i^{Int}$  and zero laxity ( $C_i^{Int} = D_i^{Int}$ ). Periodic interrupts are also modelled as zero-laxity tasks, but  $T_i^{Int}$  represents their period and they are also characterized by a release latency  $L_i^{Int}$ , which accounts for deviations from strict periodicity. For sporadic interrupts, we let  $L_i^{Int}$  equal to zero, since any variability in their arrival pattern is already accounted for by  $T_i^{Int}$ . Thus the interrupt execution demand for  $n^{Int}$  interrupts is then given by:

$$dbf_{IntO}^{part}(\tilde{P}_q, t) = \sum_{i=1}^{n^{Int}} \max\left(0, \left\lfloor \frac{t - D_i^{Int} + L_i^{Int}}{T_i^{Int}} \right\rfloor + 1\right) \cdot C_i^{Int}$$

(19)

Because the interrupt overhead increases the execution demand of a server, the  $\mathrm{dbf}^{\mathrm{part}}(\tilde{P}_q,t)$ , incorporating all the overheads, becomes:

$$dbf^{part}(\tilde{P}_{q}, t) = dbf^{part}(\tau[\tilde{P}_{q}], t) + dbf^{part}_{CpmdO}(\tilde{P}_{q}, t) + dbf^{part}_{IntO}(\tilde{P}_{q}, t)$$

(20)

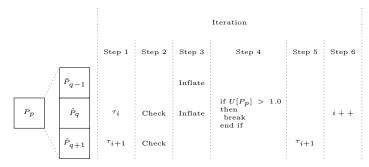

Equation 20 can be used in a new schedulability test by the algorithm that maps tasks to servers. Algorithm 1 shows the pseudo-code of this algorithm. The algorithm iterates over the set of all tasks and, for each task  $\tau_i$ , it checks whether it fits in one of the opened servers (subject to the constraints of the bin-packing heuristics used, e.g., NF or FF). For each server  $\tilde{P}_q$  checked (q being the server index), it provisionally adds task  $\tau_i$  to it, then it computes the length of the testing time interval t (computed as twice the least-common multiple of the  $T_i$  of tasks in  $\tau[\tilde{P}_q]$ )<sup>4</sup>, and finally, it applies the new schedulability test, by invoking the dbf\_part\_check function.

If the test succeeds for some server  $\tilde{P}_q$ , then task  $\tau_i$  is permanently mapped to it, otherwise, a new server is opened and task  $\tau_i$  is added to it. The task set is considered unschedulable whenever the schedulability test fails for a server with only one task.

This new algorithm is not applicable to S-EKG. In that case, for reasons that will be explained later, the task to server mapping and the server to processor assignment are performed in a single step using the algorithm that is outlined in Section 5.2.1.

To summarize, in this subsection we have developed a new overhead-aware analysis for schedulability testing in the task-to-server mapping stage. However, this test considers each server in isolation and it does not encompass all

$<sup>^4</sup>$  Approaches exist for considerably reducing the length of the testing interval t [22,40,34, 23] in order to speed up the schedulability test, but would have required some amendments, in the presence of the scheduling overheads considered.

#### **Algorithm 1** Pseudo-code of the new task-to-server mapping algorithm.

```

Input: set of n tasks \tau_i, with 1 \le i \le n

Output: set of k servers, with k \ge 0 (k = 0 means failure)

k \leftarrow 0

for i \leftarrow 1 to n do

scheduled \leftarrow 0

for q \leftarrow 1 to k do

add_task_to_server(\tau_i, \tilde{P}_q)

t \leftarrow 2 \cdot \text{lcm} \cdot \text{T}(\tilde{P}_q)

if dbf_part_check(\tilde{P}_q, t) then

scheduled \leftarrow 1

break

else

remove_task_from_server(\tau_i, \tilde{P}_q)

end if

end for

\mathbf{if}\ scheduled = 0\ \mathbf{then}

k \leftarrow k + 1 {add a new server}

add_task_to_server(\tau_i, P_k)

t \leftarrow 2 \cdot \text{lcm-T}(P_q)

if not dbf_part_check(\tilde{P}_k, t) then

k \leftarrow 0

break {failure}

end if

end if

end for

```

the scheduling overheads that may be incurred by servers when they share a processor with other servers. In the next subsection, we develop a new schedulability analysis for the processor-to-server assignment step.

#### 4.3 New demand-based schedulability test for assigning servers to processors

To fully model all the overheads incurred by the use of periodic reserves, it is necessary to assign each server to one or more processors. Precisely modelling the impact of these overheads allows us to determine the exact processing capacity requirements of each server. In turn, this allows us to test whether or not all servers can be accommodated on the m physical processors.

With the server-to-processor assignment described in Section 3, non-split servers are allocated just one processor reserve whereas split-servers must be allocated two reserves. Because, each type of server incurs different overheads, we deal with each type of server separately.

#### 4.3.1 Non-split servers

The approach we follow to check the schedulability of a server is to verify that the execution demand by all jobs assigned to a server (computed using the dbf) does not exceed the amount of time (computed using the *supply-bound*

function (sbf)) that the system can provide for their execution, for every time interval of length t. Formally, we can express this schedulability test as:

$$dbf^{sb:non-split}(\tilde{P}_q, t) \le sbf^{sb:non-split}(\tilde{P}_q, t), \forall t > 0$$

(21)

where we use the superscript "sb" (an abbreviation for "slot based") to distinguish the functions/variables used in this subsection from similar functions/variables used in the previous subsection. This superscript may be suffixed with either ":non-split" or ":split", depending on whether the function/variable applies to non-split servers or to split servers, respectively.

We develop an analysis that allows us to apply the schedulability test in Equation 21 to non-split servers in two steps. First, we revisit the analysis developed in Section 4.2 to take into account the effect of the reserve mechanism on the computing demand of a non-split server. Second, we factor into our analysis the effect of the reserve mechanism on the computing supply of a non-split server.

In Equation 20, we decomposed the demand of a server,  $\mathrm{dbf}^{\mathrm{part}}(\tilde{P}_q,t)$ , into three components. The first,  $\mathrm{dbf}^{\mathrm{part}}(\tau[\tilde{P}_q],t)$ , comprises the execution requirements induced by each task mapped to server  $\tilde{P}_q$ , including not only its execution time, but also overheads that may arise because of mechanisms used by the scheduling algorithm, i.e. timers, task releases and context switches. Clearly, these requirements are not affected by the use of reserves. However, now we also need to take into account the Release Interference,  $\mathrm{dbf}^{\mathrm{sb:non-split}}_{\mathrm{ReII}}(\tilde{P}_q,t)$ , i.e. the overhead incurred by the release of tasks mapped to other servers that share the processor with  $\tilde{P}_q$ . Furthermore, as we explain below, the other two components are also affected by the use of reserves. Hence, in a first approximation, we have:

$$dbf^{\text{sb:non-split}}(\tilde{P}_{q}, t) = dbf^{\text{part}}(\tau[\tilde{P}_{q}], t) + dbf^{\text{sb:non-split}}_{\text{CpmdO}}(\tilde{P}_{q}, t) + dbf^{\text{sb:non-split}}_{\text{ReII}}(\tilde{P}_{q}, t)$$

$$+ dbf^{\text{sb:non-split}}_{\text{IntO}}(\tilde{P}_{q}, t) + dbf^{\text{sb:non-split}}_{\text{ReII}}(\tilde{P}_{q}, t)$$

(22)

We now proceed with the development of the analytical expressions for the  $dbf^{sb:non-split}$  parameters on the right-hand side of Equation 22.

The CPMD overheads now comprise not only the preemptions caused by tasks in the server, but also the preemptions incurred due to the reserve mechanism. In the worst case, the reserve mechanism preempts the last job that executes in the server's reserve. Thus, during an interval of duration S, a non-split server incurs at most one additional preemption due to the use of reserves:

$$\operatorname{nr}_{\operatorname{pree}}^{\operatorname{sb:non-split}}(\tilde{P}_q, t) = \left\lceil \frac{t + \operatorname{Res}L}{S} \right\rceil + \operatorname{nr}_{\operatorname{pree}}^{\operatorname{part}}(\tilde{P}_q, t) \tag{23}$$

where ResL, the reserve latency, is an overhead akin to the release overheads that occurs at the beginning of a reserve and is explained later in this subsection.

Accordingly, the worst-case overall CPMD cost for that server in a time interval of length t is given by:

$$\mathrm{dbf_{CpmdO}^{sb:non-split}}(\tilde{P}_q,t) = \mathrm{nr_{pree}^{sb:non-split}}(\tilde{P}_q,t) \cdot CpmdO \tag{24}$$

Taking into account interrupts with reserves is somewhat harder than in the case of a uniprocessor. Indeed, whereas on a uniprocessor a sporadic interrupt can be modelled as a sporadic interfering task, this is not the case with reserves. This is because reserve boundaries behave like temporal firewalls, and therefore an interrupt affects only the reserve that was active at the time the interrupt task is executed. Hence, each interrupt has to be modelled as a bursty periodic task. Given the complexity of such a formulation, we deal with it in Appendix A. Let  $\mathrm{dbf}_{\mathrm{IntO}}^{\mathrm{sb:non-split}}(\tilde{P}_q,t)$  denote the amount of time required for executing all fired interrupts inside the reserves of  $\tilde{P}_q$  in a time interval of length t, as determined in Appendix A.

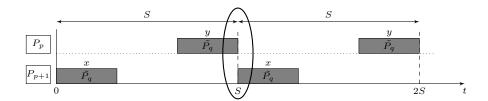

Finally, we consider the release overhead, i.e. the processor time required to handle the release of jobs. On slot-based task-splitting algorithms, a server's tasks share the processor with other tasks whose servers are assigned to the same processor. Consistent with implementation [38,39] we assume that all jobs of a task are released on the processor(s) to which the task is assigned. As shown in Figure 6, non-split server  $\tilde{P}_q$  can incur not only the release overheads of its own jobs, but also the release overheads of the jobs of both its immediate neighbor servers ( $\tilde{P}_{q-1}$  and  $\tilde{P}_{q+1}$ ).

Fig. 6: Illustration of the release interference for non-split servers. In this example, server  $\tilde{P}_q$  may suffer the interference from the release of tasks mapped to  $\tilde{P}_{q-1}$  and  $\tilde{P}_{q+1}$ , if these releases occur within  $\tilde{P}_q$ 's reserve.

Recall that the release overhead cost of all jobs of  $\tau[\tilde{P}_q]$  in a time interval of length t is already accounted for in the derivation of  $\mathrm{dbf}^{\mathrm{part}}(\tau[\tilde{P}_q],t)$  (see Equation 14). Therefore, what remains is to incorporate the release interference,  $\mathrm{dbf}^{\mathrm{sb:non-split}}_{\mathrm{ReII}}(\tilde{P}_q,t)$ , the release overhead cost from neighboring servers, i.e. servers sharing the same processor:

$$dbf_{\text{ReII}}^{\text{sb:non-split}}(\tilde{P}_q, t) = dbf_{\text{ReIO}}^{\text{part}}(\tilde{P}_{q-1}, t) + dbf_{\text{ReIO}}^{\text{part}}(\tilde{P}_{q+1}, t)$$

(25)

where  $\mathrm{dbf}^{\mathrm{part}}_{\mathrm{RelO}}(\tilde{P}_q,t)$  (see Equation 13) denotes the amount of time required to release all jobs of server  $\tilde{P}_q$  in a time interval of length t.

We now consider the effect of the reserve mechanism on the amount of time supplied to the execution of the tasks of a non-split server. In comparison with the analysis in Section 4.2, the amount of time supplied to the execution of a non-split server is reduced because of two factors. The first is the sharing of the processor with other servers. The second is the imprecision of the timers used to measure the duration of the reserves. We analyze the effect of each of these factors in turn.

In slot-based task-splitting algorithms, a non-split server  $\tilde{P}_q$  is confined to execute within a single periodic reserve of length  $Res^{len}[\tilde{P}_q]$ , which is available every S time units:

$$Res^{len}[\tilde{P}_q] = U^{infl}[\tilde{P}_q] \cdot S$$

(26)

where  $U^{infl}[\tilde{P}_q]$  represents the inflated processing capacity of server  $\tilde{P}_q$ , which is computed by Algorithm 2 presented at the end of this subsection. Thus, for any time interval of length t, only a fraction of such interval is supplied for the execution of a server. We model the unavailability of the reserve as an interfering  $fake\ task$  with attributes:

$$C^{fake} = S - Res^{len}[\tilde{P}_q]$$

$$T^{fake} = S$$

$$D^{fake} = C^{fake}$$

(27)

Hence, the supply-bound function for non-split servers can be expressed, in a first approximation, as follows:

$$\operatorname{sbf^{sb:non-split}}(\tilde{P}_q, t) = t - \max\left(0, \left\lfloor \frac{t - D^{fake}}{T^{fake}} \right\rfloor + 1\right) \cdot C^{fake}$$

(28)

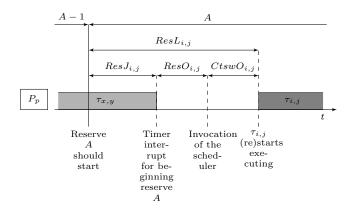

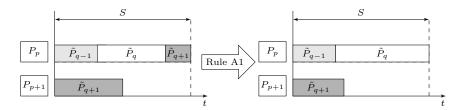

The second source of the reduction in the amount of time supplied to the execution of a non-split server is the processing time required to switch from one reserve to the next, which also includes the execution of the scheduler. Furthermore, the switch of reserves is also associated with a delay between the time at which the current reserve should end and the time at which it actually ends, for example because the processor is executing a non-preemptible code segment. To facilitate the experimental measurement of this overhead, we decide to group these three parameters in a single one that we call reserve latency. This is illustrated in Figure 7, which also shows that this parameter includes the time required to switch to the first job of the new reserve.

We model this reduction in the supply of processing time to the reserve as an increase in the execution demand of the fake task. Let ResL be an upper bound for the reserve latency. The expression for  ${\rm sbf^{sb:non-split}}(\tilde{P}_q,t)$  then becomes:

Fig. 7: Illustration of the reserve overhead. The execution of job  $\tau_{i,j}$  of server mapped to reserve A, is delayed by ResL with respect to the instant the reserve should start.

$$\mathrm{sbf^{sb:non-split}}(\tilde{P}_q, t) = t - \max\left(0, \left\lfloor \frac{t - D^{fake} + ResL}{T^{fake}} \right\rfloor + 1\right) \cdot (C^{fake} + ResL) \tag{29}$$

By replacing this expression in Inequality 21 and moving some terms from the right-hand side to the left-hand side, we obtain the following schedulability test for non-split servers:

$$\mathrm{dbf^{sb:non-split}}(\tilde{P}_q,t) + \mathrm{dbf^{sb:non-split}_{Fake}}(\tilde{P}_q,t) \leq t, \forall t > 0 \tag{30}$$

where dbf<sup>sb:non-split</sup> $(\tilde{P}_q,t)$  is given by Equation 22 and dbf<sup>sb:non-split</sup><sub>Fake</sub> $(\tilde{P}_q,t)$  is given by:

$$dbf_{Fake}^{sb:non-split}(\tilde{P}_q, t) = \max\left(0, \left\lfloor \frac{t - D^{fake} + ResL}{T^{fake}} \right\rfloor + 1\right) \cdot (C^{fake} + ResL)$$

(31)

To complete the analysis of non-split servers, we provide an algorithm to compute the inflated utilization of server  $\tilde{P}_q$ ,  $U^{infl}[\tilde{P}_q]$ . Indeed, evaluating  $\mathrm{dbf_{Fake}^{sb:non-split}}(\tilde{P}_q,t)$  depends on  $U^{infl}[\tilde{P}_q]$ , via  $Res^{len}[\tilde{P}_q]$  and  $C^{fake}$  (see Equations. 26 and 27). Furthermore,  $\mathrm{dbf_{IntO}^{sb:non-split}}(\tilde{P}_q,t)$  also depends on  $U^{infl}[\tilde{P}_q]$ , as shown in Appendix A.

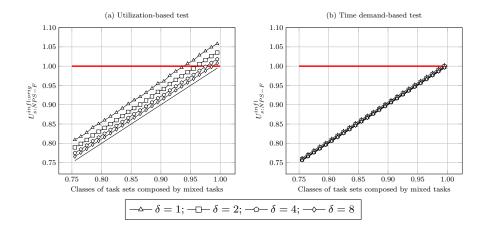

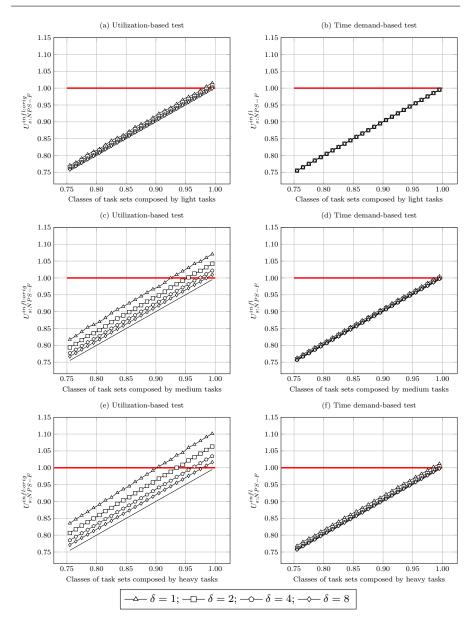

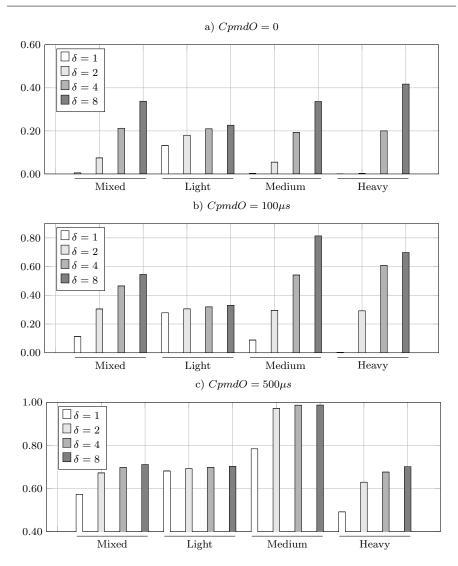

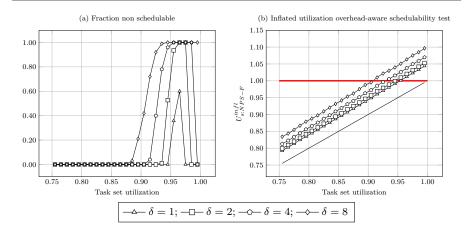

In order to achieve the highest possible schedulability, we are interested in determining the minimum inflated utilization required for server  $\tilde{P}_q$ . We use the schedulability test developed in this section to determine an interval that is guaranteed to include the inflated utilization. This interval can be arbitrarily small. We start with the interval  $[U[\tilde{P}_q], 1.0]$ . Then, like in the bisection method, we successively halve this interval in such a way that the inflated utilization is guaranteed to be in every generated interval. Algorithm 2 shows the pseudo-code for the inflate\_sb\_non\_split function. In each iteration, it